IBM POWER

Encyclopedia

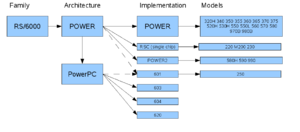

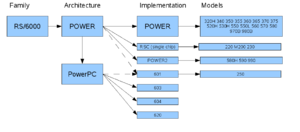

POWER is a reduced instruction set computer

(RISC) instruction set architecture (ISA) developed by IBM

. The name is an acronym for Performance Optimization With Enhanced RISC.

POWER is also the name of a series of microprocessors that implement the POWER ISA. The POWER series microprocessors are used as the CPU in many of IBM's servers, minicomputers, workstations, and supercomputers. The POWER3

and subsequent microprocessors in the POWER series all implement the full 64-bit

PowerPC

architecture. The POWER3 and above do not implement any of the old POWER instructions that were removed from the ISA when the PowerPC ISA came out, nor any of the POWER2 extensions such as

Appendix E of Book I: PowerPC User Instruction Set Architecture of PowerPC Architecture Book, Version 2.02 describes the differences between the POWER and POWER2 instruction set architectures and the version of the PowerPC instruction set architecture implemented by the POWER5.

started a project with a design objective of creating a large telephone-switching network with a potential capacity to deal with at least 300 calls per second. It was projected that 20,000 machine instructions would be required to handle each call while maintaining a real-time response, so a processor with a performance of 12 MIPS was deemed necessary. This requirement was extremely ambitious for the time, but it was realised that much of the complexity of contemporary CPUs could be dispensed with, since this machine would need only to perform I/O, branches, add register-register, move data between registers and memory, and would have no need for special instructions to perform heavy arithmetic.

This simple design philosophy, whereby each step of a complex operation is specified explicitly by one machine instruction, and all instructions are required to complete in the same constant time, would later come to be known as RISC.

By 1975 the telephone switch project was canceled without a prototype. From the estimates from simulations produced in the project's first year, however, it looked as if the processor being designed for this project could be a very promising general-purpose processor, so work continued at Thomas J. Watson Research Center

building #801, on the 801 project.

Model 91 and the CDC 6600

(although the Model 91 had been based on a CISC design), to determine if a RISC machine could maintain multiple instructions per cycle, or what design changes need to be made to the 801 design to allow for multiple-execution-units.

To increase performance, Cheetah had separate branch, fixed-point, and floating-point execution units. Many changes were made to the 801 design to allow for multiple-execution-units. Cheetah was originally planned to be manufactured using bipolar

emitter-coupled logic

(ECL) technology, but by 1984 complementary metal–oxide–semiconductor (CMOS

) technology afforded an increase in the level of circuit integration while improving transistor-logic performance.

series, based on that architecture.

Sometime between the years of 1990-95, the project was considered overly ambitious and was canceled.

. These RS/6000 computers were divided into two classes, workstation

s and server

s, and hence introduced as the POWERstation and POWERserver. The RS/6000 CPU had 2 configurations, called the "RIOS-1" and "RIOS.9" (or more commonly the "POWER1

" CPU). A RIOS-1 configuration had a total of 10 discrete chips - an instruction cache chip, fixed-point chip, floating-point chip, 4 data cache chips, storage control chip, input/output chips, and a clock chip. The lower cost RIOS.9 configuration had 8 discrete chips - an instruction cache chip, fixed-point chip, floating-point chip, 2 data cache chips, storage control chip, input/output chip, and a clock chip.

A single-chip implementation of RIOS, RSC (for "RISC Single Chip

"), was developed for lower-end RS/6000's; the first machines using RSC were released in 1992.

. The AS/400 engineering team at IBM was designing a RISC instruction set to replace the CISC instruction set of the existing AS/400 computers. Their original design was a variant of the existing "IMPI" instruction set, extended to 64 bits and given some RISC instructions to speed up the more computationally intensive commercial applications that were being put on AS/400s. IBM management wanted them to use PowerPC, but they resisted, arguing that the existing 32/64-bit PowerPC instruction set would not enable a viable transition for OS/400 software and that the existing instruction set required extensions for the commercial applications on the AS/400. Eventually, an extension to the PowerPC instruction set, called "Amazon", was developed.

At the same time, the RS/6000

developers were broadly expanding their product line to include systems which spanned from low-end workstations, to mainframe competitor-large enterprise SMP systems, to clustered RS/6000-SP2 supercomputing systems. PowerPC processors developed in the AIM alliance

suited the low-end RISC workstation and small server space well. But mainframe and large clustered supercomputing systems required more performance and RAS features than processors designed for Apple Power Macs. Multiple processor designs were required to simultaneously meet the requirements of the cost-focused Apple Power Mac, high-performance and RAS RS/6000 systems, and the AS/400 transition to PowerPC.

Amazon was extended to support those features as well, so that processors could be designed for use in both high-end RS/6000 and AS/400 machines.

The project to develop the first such processor was "Bellatrix" (the name of a star in the Orion constellation

, also called the "Amazon Star"). The Bellatrix project was extremely ambitious in its pervasive use of self-timed & pulse based circuits and the EDA tools required to support this design strategy, and was eventually terminated. To address technical workstation, supercomputer, and engineering/scientific markets, IBM Austin (the home of the RS/6000s) then started developing a time-to-market single-chip version of the Power2 (P2SC) in parallel with the development of a sophisticated 64-bit PowerPC processor with the POWER2 extensions and twin sophisticated MAF floating point units (the POWER3/630). To address RS/6000 commercial applications and AS/400 systems, IBM Rochester (the home of the AS/400s) started developing the first of the high-end 64-bit PowerPC processors with AS/400 extensions, and IBM Endicott started developing a low-end single-chip PowerPC processor with AS/400 extensions.

processor effort as a successor to the POWER1 two years before the creation of the 1991 Apple/IBM/Motorola alliance in Austin, Texas. Despite being impacted by diversion of resources to jump start the Apple/IBM/Motorola effort, the POWER2 took five years from start to system shipment. By adding a second fixed-point unit, a second floating point unit

, and other performance enhancements to the design, the POWER2 had leadership performance when it was announced in November 1993.

New instructions were also added to the instruction set:

To support the RS/6000 and RS/6000 SP2 product lines in 1996, IBM had its own design team implement a single-chip version of POWER2, the P2SC ("POWER2 Super Chip"), outside the Apple/IBM/Motorola alliance in IBM's most advanced and dense CMOS-6S process. P2SC combined all of the separate POWER2 instruction cache, fixed point, floating point, storage control, and data cache chips onto one huge die. At the time of its introduction, P2SC was the largest and highest transistor count processor in the industry. Despite the challenge of its size, complexity, and advanced CMOS process, the first tape-out version of the processor was able to be shipped, and it had leadership floating point performance at the time it was announced. P2SC was the processor used in the 1997 IBM Deep Blue chess playing supercomputer which beat chess grandmaster Garry Kasparov

. With its twin sophisticated MAF floating point units and huge wide and low latency memory interfaces, P2SC was primarily targeted at engineering and scientific applications. P2SC was eventually succeeded by the POWER3, which included 64-bit, SMP capability, and a full transition to PowerPC in addition to P2SC's sophisticated twin MAF floating point units.

's largest customers of desktop-class microprocessors, asked Motorola to join the discussions because of their long relationship, their more extensive experience with manufacturing high-volume microprocessors than IBM, and to serve as a second source for the microprocessor

s. This three-way collaboration, based in Austin, Texas

, became known as the AIM alliance

, for Apple, IBM, Motorola.

After two years of development, the resulting PowerPC

architecture was introduced in 1993. A modified version of the RSC architecture, PowerPC added single-precision floating point instructions and general register-to-register multiply and divide instructions, and removed some POWER features such as the specialized multiply and divide instructions using the MQ register. It also added a 64-bit version of the architecture and support for SMP

.

processor in 1998. It implemented the 64-bit PowerPC instruction set, including all of the optional instructions of the ISA (at the time). All subsequent POWER processors implemented the full 64-bit PowerPC and POWER instruction sets, so that there were no longer any IBM processors that implemented only POWER or only POWER2.

processor, the first in the GIGA-Series, in 2001. Like the POWER3, it was a full 64-bit processor, implementing the full 64-bit PowerPC instruction set; it also had the AS/400 extensions, and was used in both RS/6000 and AS/400 systems, replacing both POWER3 and the RS64 processors. There was a new ISA release at this point called the PowerPC 2.00 ISA, which added a couple of extensions to the ISA, such as a version of mfcr which also took a field argument.

IBM introduced the POWER5

IBM introduced the POWER5

processor in 2004. It is a dual-core

processor with support for simultaneous multithreading

with two threads, so it implements 4 logical processors. Using the Virtual Vector Architecture

, several POWER5 processors can act together as one vector processor

. The POWER5 added more instructions to the ISA.

The POWER5+ added even more instructions, bringing the ISA to version 2.02.

was announced on May 21, 2007. It adds VMX

to the POWER series. It also introduces the second generation of IBM ViVA

, ViVA-2. It is a dual-core design, reaching 5.0 GHz at 65 nm. It has very advanced interchip communication technology. Its power consumption is nearly the same as the preceding POWER5, whilst offering doubled performance.

was released in February 2010 and was a substantial evolution from the POWER6

design, focusing more on power efficiency through multiple cores and simultaneous multithreading.

While the POWER6 features a dual-core processor, each capable of two-way simultaneous multithreading (SMT), the IBM POWER7 processor has eight cores, and four threads per core, for a total capacity of 32 simultaneous threads. Its power consumption is similar to the preceding POWER6, while quadrupling the number of cores, with each core having higher performance.

The POWER design is descended directly from the earlier 801 CPU, widely considered to be the first true RISC processor design. The 801 was used in a number of applications inside IBM hardware.

The POWER design is descended directly from the earlier 801 CPU, widely considered to be the first true RISC processor design. The 801 was used in a number of applications inside IBM hardware.

At about the same time the PC/RT was being released, IBM started the America Project, to design the most powerful CPU on the market. They were interested primarily in fixing two problems in the 801 design:

Floating point

became a focus for the America Project, and IBM was able to use new algorithms developed in the early 1980s that could support 64-bit double-precision multiplies and divides in a single cycle. The FPU

portion of the design was separate from the instruction decoder and integer parts, allowing the decoder to send instructions to both the FPU and ALU

(integer) execution unit

s at the same time. IBM complemented this with a complex instruction decoder which could be fetching one instruction, decoding another, and sending one to the ALU and FPU at the same time, resulting in one of the first superscalar

CPU designs in use.

The system used 32 32-bit integer

register

s and another 32 64-bit floating point registers, each in their own unit. The branch unit also included a number of "private" registers for its own use, including the program counter

.

Another interesting feature of the architecture is a virtual address system which maps all addresses into a 52-bit space. In this way applications can share memory in a "flat" 32-bit space, and all of the programs can have different blocks of 32 bits each.

Reduced instruction set computer

Reduced instruction set computing, or RISC , is a CPU design strategy based on the insight that simplified instructions can provide higher performance if this simplicity enables much faster execution of each instruction. A computer based on this strategy is a reduced instruction set computer...

(RISC) instruction set architecture (ISA) developed by IBM

IBM

International Business Machines Corporation or IBM is an American multinational technology and consulting corporation headquartered in Armonk, New York, United States. IBM manufactures and sells computer hardware and software, and it offers infrastructure, hosting and consulting services in areas...

. The name is an acronym for Performance Optimization With Enhanced RISC.

POWER is also the name of a series of microprocessors that implement the POWER ISA. The POWER series microprocessors are used as the CPU in many of IBM's servers, minicomputers, workstations, and supercomputers. The POWER3

POWER3

The POWER3 is a microprocessor, designed and exclusively manufactured by IBM, that implemented the 64-bit version of the PowerPC instruction set architecture , including all of the optional instructions of the ISA such as the POWER2. It was introduced on 5 October 1998, debuting in the RS/6000 43P...

and subsequent microprocessors in the POWER series all implement the full 64-bit

64-bit

64-bit is a word size that defines certain classes of computer architecture, buses, memory and CPUs, and by extension the software that runs on them. 64-bit CPUs have existed in supercomputers since the 1970s and in RISC-based workstations and servers since the early 1990s...

PowerPC

PowerPC

PowerPC is a RISC architecture created by the 1991 Apple–IBM–Motorola alliance, known as AIM...

architecture. The POWER3 and above do not implement any of the old POWER instructions that were removed from the ISA when the PowerPC ISA came out, nor any of the POWER2 extensions such as

lfq or stfq.Appendix E of Book I: PowerPC User Instruction Set Architecture of PowerPC Architecture Book, Version 2.02 describes the differences between the POWER and POWER2 instruction set architectures and the version of the PowerPC instruction set architecture implemented by the POWER5.

The 801 research project

In 1974, IBMIBM

International Business Machines Corporation or IBM is an American multinational technology and consulting corporation headquartered in Armonk, New York, United States. IBM manufactures and sells computer hardware and software, and it offers infrastructure, hosting and consulting services in areas...

started a project with a design objective of creating a large telephone-switching network with a potential capacity to deal with at least 300 calls per second. It was projected that 20,000 machine instructions would be required to handle each call while maintaining a real-time response, so a processor with a performance of 12 MIPS was deemed necessary. This requirement was extremely ambitious for the time, but it was realised that much of the complexity of contemporary CPUs could be dispensed with, since this machine would need only to perform I/O, branches, add register-register, move data between registers and memory, and would have no need for special instructions to perform heavy arithmetic.

This simple design philosophy, whereby each step of a complex operation is specified explicitly by one machine instruction, and all instructions are required to complete in the same constant time, would later come to be known as RISC.

By 1975 the telephone switch project was canceled without a prototype. From the estimates from simulations produced in the project's first year, however, it looked as if the processor being designed for this project could be a very promising general-purpose processor, so work continued at Thomas J. Watson Research Center

Thomas J. Watson Research Center

The Thomas J. Watson Research Center is the headquarters for the IBM Research Division.The center is on three sites, with the main laboratory in Yorktown Heights, New York, 38 miles north of New York City, a building in Hawthorne, New York, and offices in Cambridge, Massachusetts.- Overview :The...

building #801, on the 801 project.

1982 Cheetah project

For two years at the Watson Research Center, the superscalar limits of the 801 design were explored, such as the feasibility of implementing the design using multiple functional units to improve performance, similar to what had been done in the IBM System/360System/360

The IBM System/360 was a mainframe computer system family first announced by IBM on April 7, 1964, and sold between 1964 and 1978. It was the first family of computers designed to cover the complete range of applications, from small to large, both commercial and scientific...

Model 91 and the CDC 6600

CDC 6600

The CDC 6600 was a mainframe computer from Control Data Corporation, first delivered in 1964. It is generally considered to be the first successful supercomputer, outperforming its fastest predecessor, IBM 7030 Stretch, by about three times...

(although the Model 91 had been based on a CISC design), to determine if a RISC machine could maintain multiple instructions per cycle, or what design changes need to be made to the 801 design to allow for multiple-execution-units.

To increase performance, Cheetah had separate branch, fixed-point, and floating-point execution units. Many changes were made to the 801 design to allow for multiple-execution-units. Cheetah was originally planned to be manufactured using bipolar

Bipolar junction transistor

|- align = "center"| || PNP|- align = "center"| || NPNA bipolar transistor is a three-terminal electronic device constructed of doped semiconductor material and may be used in amplifying or switching applications. Bipolar transistors are so named because their operation involves both electrons...

emitter-coupled logic

Emitter-coupled logic

In electronics, emitter-coupled logic , is a logic family that achieves high speed by using an overdriven BJT differential amplifier with single-ended input, whose emitter current is limited to avoid the slow saturation region of transistor operation....

(ECL) technology, but by 1984 complementary metal–oxide–semiconductor (CMOS

CMOS

Complementary metal–oxide–semiconductor is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits...

) technology afforded an increase in the level of circuit integration while improving transistor-logic performance.

The America project

In 1985, research on a second-generation RISC architecture started at the IBM Thomas J. Watson Research Center, producing the "AMERICA architecture"; in 1986, IBM Austin started developing the RS/6000RS/6000

RISC System/6000, or RS/6000 for short, is a family of RISC and UNIX based servers, workstations and supercomputers made by IBM in the 1990s. The RS/6000 family replaced the IBM RT computer platform in February 1990 and was the first computer line to see the use of IBM's POWER and PowerPC based...

series, based on that architecture.

The Bellatrix project

Sometime in the years of 1986-89, the Bellatrix project was started, with the premise of using the America architecture as the base for a common architecture that could host OS/390 for mainframe applications, OS/400 for multi-processor server transactional processing, and AIX for scientific applications.Sometime between the years of 1990-95, the project was considered overly ambitious and was canceled.

POWER

In February 1990, the first computers from IBM to incorporate the POWER Architecture ("Performance Optimized With Enhanced RISC") were called the "RISC System/6000" or RS/6000RS/6000

RISC System/6000, or RS/6000 for short, is a family of RISC and UNIX based servers, workstations and supercomputers made by IBM in the 1990s. The RS/6000 family replaced the IBM RT computer platform in February 1990 and was the first computer line to see the use of IBM's POWER and PowerPC based...

. These RS/6000 computers were divided into two classes, workstation

Workstation

A workstation is a high-end microcomputer designed for technical or scientific applications. Intended primarily to be used by one person at a time, they are commonly connected to a local area network and run multi-user operating systems...

s and server

Server (computing)

In the context of client-server architecture, a server is a computer program running to serve the requests of other programs, the "clients". Thus, the "server" performs some computational task on behalf of "clients"...

s, and hence introduced as the POWERstation and POWERserver. The RS/6000 CPU had 2 configurations, called the "RIOS-1" and "RIOS.9" (or more commonly the "POWER1

POWER1

The POWER1 is a multi-chip CPU developed and fabricated by IBM that implemented the POWER instruction set architecture . It was originally known as the “RISC System/6000 CPU” or when an abbreviated form, the “RS/6000 CPU” before introduction of successors required the original name to be replaced...

" CPU). A RIOS-1 configuration had a total of 10 discrete chips - an instruction cache chip, fixed-point chip, floating-point chip, 4 data cache chips, storage control chip, input/output chips, and a clock chip. The lower cost RIOS.9 configuration had 8 discrete chips - an instruction cache chip, fixed-point chip, floating-point chip, 2 data cache chips, storage control chip, input/output chip, and a clock chip.

A single-chip implementation of RIOS, RSC (for "RISC Single Chip

RISC Single Chip

The RISC Single Chip, or RSC, is a single-chip microprocessor developed and fabricated by International Business Machines . The RSC was a feature-reduced single-chip implementation of the POWER1, a multi-chip central processing unit which implemented the POWER instruction set architecture...

"), was developed for lower-end RS/6000's; the first machines using RSC were released in 1992.

The Amazon project

In 1990 the Amazon project was started to create a common architecture that would host both AIX and OS/400OS/400

IBM i is an EBCDIC based operating system that runs on IBM Power Systems. It is the current evolution of the operating system named i5/OS which was originally named OS/400 when it was introduced with the AS/400 computer system in 1988....

. The AS/400 engineering team at IBM was designing a RISC instruction set to replace the CISC instruction set of the existing AS/400 computers. Their original design was a variant of the existing "IMPI" instruction set, extended to 64 bits and given some RISC instructions to speed up the more computationally intensive commercial applications that were being put on AS/400s. IBM management wanted them to use PowerPC, but they resisted, arguing that the existing 32/64-bit PowerPC instruction set would not enable a viable transition for OS/400 software and that the existing instruction set required extensions for the commercial applications on the AS/400. Eventually, an extension to the PowerPC instruction set, called "Amazon", was developed.

At the same time, the RS/6000

RS/6000

RISC System/6000, or RS/6000 for short, is a family of RISC and UNIX based servers, workstations and supercomputers made by IBM in the 1990s. The RS/6000 family replaced the IBM RT computer platform in February 1990 and was the first computer line to see the use of IBM's POWER and PowerPC based...

developers were broadly expanding their product line to include systems which spanned from low-end workstations, to mainframe competitor-large enterprise SMP systems, to clustered RS/6000-SP2 supercomputing systems. PowerPC processors developed in the AIM alliance

AIM alliance

The AIM alliance was an alliance formed on October 2, 1991, between Apple Inc. , IBM, and Motorola to create a new computing standard based on the PowerPC architecture. The stated goal of the alliance was to challenge the dominant Wintel computing platform with a new computer design and a...

suited the low-end RISC workstation and small server space well. But mainframe and large clustered supercomputing systems required more performance and RAS features than processors designed for Apple Power Macs. Multiple processor designs were required to simultaneously meet the requirements of the cost-focused Apple Power Mac, high-performance and RAS RS/6000 systems, and the AS/400 transition to PowerPC.

Amazon was extended to support those features as well, so that processors could be designed for use in both high-end RS/6000 and AS/400 machines.

The project to develop the first such processor was "Bellatrix" (the name of a star in the Orion constellation

Gamma Orionis

Bellatrix, also known by its Bayer designation Gamma Orionis , is the third brightest star in the constellation Orion, the twenty-seventh brightest star in the night sky, and one of the brightest second-magnitude stars....

, also called the "Amazon Star"). The Bellatrix project was extremely ambitious in its pervasive use of self-timed & pulse based circuits and the EDA tools required to support this design strategy, and was eventually terminated. To address technical workstation, supercomputer, and engineering/scientific markets, IBM Austin (the home of the RS/6000s) then started developing a time-to-market single-chip version of the Power2 (P2SC) in parallel with the development of a sophisticated 64-bit PowerPC processor with the POWER2 extensions and twin sophisticated MAF floating point units (the POWER3/630). To address RS/6000 commercial applications and AS/400 systems, IBM Rochester (the home of the AS/400s) started developing the first of the high-end 64-bit PowerPC processors with AS/400 extensions, and IBM Endicott started developing a low-end single-chip PowerPC processor with AS/400 extensions.

POWER2

IBM started the POWER2POWER2

The POWER2, originally named RIOS2, is a processor designed by IBM that implemented the POWER instruction set architecture. The POWER2 was the successor of the POWER1, debuting in September 1993 within IBM's RS/6000 systems. When introduced, the POWER2 was the fastest microprocessor, surpassing the...

processor effort as a successor to the POWER1 two years before the creation of the 1991 Apple/IBM/Motorola alliance in Austin, Texas. Despite being impacted by diversion of resources to jump start the Apple/IBM/Motorola effort, the POWER2 took five years from start to system shipment. By adding a second fixed-point unit, a second floating point unit

Floating point unit

A floating-point unit is a part of a computer system specially designed to carry out operations on floating point numbers. Typical operations are addition, subtraction, multiplication, division, and square root...

, and other performance enhancements to the design, the POWER2 had leadership performance when it was announced in November 1993.

New instructions were also added to the instruction set:

- Quad-word storage instructions. The quad-word load instruction moves two adjacent double-precision values into two adjacent floating-point registers.

- Hardware square root instruction.

- Floating-point to integer conversion instructions.

To support the RS/6000 and RS/6000 SP2 product lines in 1996, IBM had its own design team implement a single-chip version of POWER2, the P2SC ("POWER2 Super Chip"), outside the Apple/IBM/Motorola alliance in IBM's most advanced and dense CMOS-6S process. P2SC combined all of the separate POWER2 instruction cache, fixed point, floating point, storage control, and data cache chips onto one huge die. At the time of its introduction, P2SC was the largest and highest transistor count processor in the industry. Despite the challenge of its size, complexity, and advanced CMOS process, the first tape-out version of the processor was able to be shipped, and it had leadership floating point performance at the time it was announced. P2SC was the processor used in the 1997 IBM Deep Blue chess playing supercomputer which beat chess grandmaster Garry Kasparov

Garry Kasparov

Garry Kimovich Kasparov is a Russian chess grandmaster, a former World Chess Champion, writer, political activist, and one of the greatest chess players of all time....

. With its twin sophisticated MAF floating point units and huge wide and low latency memory interfaces, P2SC was primarily targeted at engineering and scientific applications. P2SC was eventually succeeded by the POWER3, which included 64-bit, SMP capability, and a full transition to PowerPC in addition to P2SC's sophisticated twin MAF floating point units.

PowerPC

At some point in 1991, Apple Computer decided to not migrate their 68000-based software and hardware to Motorola's next generation 88xxx series microprocessor. Soon after, Apple, as one of MotorolaMotorola

Motorola, Inc. was an American multinational telecommunications company based in Schaumburg, Illinois, which was eventually divided into two independent public companies, Motorola Mobility and Motorola Solutions on January 4, 2011, after losing $4.3 billion from 2007 to 2009...

's largest customers of desktop-class microprocessors, asked Motorola to join the discussions because of their long relationship, their more extensive experience with manufacturing high-volume microprocessors than IBM, and to serve as a second source for the microprocessor

Microprocessor

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit, or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and...

s. This three-way collaboration, based in Austin, Texas

Austin, Texas

Austin is the capital city of the U.S. state of :Texas and the seat of Travis County. Located in Central Texas on the eastern edge of the American Southwest, it is the fourth-largest city in Texas and the 14th most populous city in the United States. It was the third-fastest-growing large city in...

, became known as the AIM alliance

AIM alliance

The AIM alliance was an alliance formed on October 2, 1991, between Apple Inc. , IBM, and Motorola to create a new computing standard based on the PowerPC architecture. The stated goal of the alliance was to challenge the dominant Wintel computing platform with a new computer design and a...

, for Apple, IBM, Motorola.

After two years of development, the resulting PowerPC

PowerPC

PowerPC is a RISC architecture created by the 1991 Apple–IBM–Motorola alliance, known as AIM...

architecture was introduced in 1993. A modified version of the RSC architecture, PowerPC added single-precision floating point instructions and general register-to-register multiply and divide instructions, and removed some POWER features such as the specialized multiply and divide instructions using the MQ register. It also added a 64-bit version of the architecture and support for SMP

Symmetric multiprocessing

In computing, symmetric multiprocessing involves a multiprocessor computer hardware architecture where two or more identical processors are connected to a single shared main memory and are controlled by a single OS instance. Most common multiprocessor systems today use an SMP architecture...

.

POWER3

IBM introduced the POWER3POWER3

The POWER3 is a microprocessor, designed and exclusively manufactured by IBM, that implemented the 64-bit version of the PowerPC instruction set architecture , including all of the optional instructions of the ISA such as the POWER2. It was introduced on 5 October 1998, debuting in the RS/6000 43P...

processor in 1998. It implemented the 64-bit PowerPC instruction set, including all of the optional instructions of the ISA (at the time). All subsequent POWER processors implemented the full 64-bit PowerPC and POWER instruction sets, so that there were no longer any IBM processors that implemented only POWER or only POWER2.

POWER4

IBM introduced the POWER4POWER4

The POWER4 is a microprocessor developed by International Business Machines that implemented the 64-bit PowerPC and PowerPC AS instruction set architectures. Released in 2001, the POWER4 succeeded the POWER3 and RS64 microprocessors, and was used in RS/6000 and AS/400 computers, ending a separate...

processor, the first in the GIGA-Series, in 2001. Like the POWER3, it was a full 64-bit processor, implementing the full 64-bit PowerPC instruction set; it also had the AS/400 extensions, and was used in both RS/6000 and AS/400 systems, replacing both POWER3 and the RS64 processors. There was a new ISA release at this point called the PowerPC 2.00 ISA, which added a couple of extensions to the ISA, such as a version of mfcr which also took a field argument.

POWER5

POWER5

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the highly successful POWER4. The principal improvements are support for simultaneous multithreading and an on-die memory controller...

processor in 2004. It is a dual-core

Multi-core (computing)

A multi-core processor is a single computing component with two or more independent actual processors , which are the units that read and execute program instructions...

processor with support for simultaneous multithreading

Simultaneous multithreading

Simultaneous multithreading, often abbreviated as SMT, is a technique for improving the overall efficiency of superscalar CPUs with hardware multithreading...

with two threads, so it implements 4 logical processors. Using the Virtual Vector Architecture

IBM ViVA

ViVA is a technology from IBM for coupling together multiple scalar floating point units to act as a single vector processor...

, several POWER5 processors can act together as one vector processor

Vector processor

A vector processor, or array processor, is a central processing unit that implements an instruction set containing instructions that operate on one-dimensional arrays of data called vectors. This is in contrast to a scalar processor, whose instructions operate on single data items...

. The POWER5 added more instructions to the ISA.

The POWER5+ added even more instructions, bringing the ISA to version 2.02.

POWER6

POWER6POWER6

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.03. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor...

was announced on May 21, 2007. It adds VMX

AltiVec

AltiVec is a floating point and integer SIMD instruction set designed and owned by Apple, IBM and Freescale Semiconductor, formerly the Semiconductor Products Sector of Motorola, , and implemented on versions of the PowerPC including Motorola's G4, IBM's G5 and POWER6 processors, and P.A. Semi's...

to the POWER series. It also introduces the second generation of IBM ViVA

IBM ViVA

ViVA is a technology from IBM for coupling together multiple scalar floating point units to act as a single vector processor...

, ViVA-2. It is a dual-core design, reaching 5.0 GHz at 65 nm. It has very advanced interchip communication technology. Its power consumption is nearly the same as the preceding POWER5, whilst offering doubled performance.

POWER7

POWER7POWER7

POWER7 is a Power Architecture microprocessor released in 2010 that succeeded the POWER6. POWER7 was developed by IBM at several sites including IBM's Rochester, MN; Austin, TX; Essex Junction, Vermont; T. J. Watson Research Center, NY; Bromont, QC and Böblingen, Germany laboratories...

was released in February 2010 and was a substantial evolution from the POWER6

POWER6

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.03. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor...

design, focusing more on power efficiency through multiple cores and simultaneous multithreading.

While the POWER6 features a dual-core processor, each capable of two-way simultaneous multithreading (SMT), the IBM POWER7 processor has eight cores, and four threads per core, for a total capacity of 32 simultaneous threads. Its power consumption is similar to the preceding POWER6, while quadrupling the number of cores, with each core having higher performance.

POWER8

Future successor to POWER7 currently under development with focus on improved SMT, reliability, larger caches, accelerators and more cores. It will be built on a 22 nm process at an unknown date.The architecture

At about the same time the PC/RT was being released, IBM started the America Project, to design the most powerful CPU on the market. They were interested primarily in fixing two problems in the 801 design:

- The 801 required all instructions to complete in one clock cycle, which precluded floating pointFloating pointIn computing, floating point describes a method of representing real numbers in a way that can support a wide range of values. Numbers are, in general, represented approximately to a fixed number of significant digits and scaled using an exponent. The base for the scaling is normally 2, 10 or 16...

instructions. - Although the decoder was pipelined as a side effect of these single-cycle operations, they didn't use superscalarSuperscalarA superscalar CPU architecture implements a form of parallelism called instruction level parallelism within a single processor. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate...

effects.

Floating point

Floating point

In computing, floating point describes a method of representing real numbers in a way that can support a wide range of values. Numbers are, in general, represented approximately to a fixed number of significant digits and scaled using an exponent. The base for the scaling is normally 2, 10 or 16...

became a focus for the America Project, and IBM was able to use new algorithms developed in the early 1980s that could support 64-bit double-precision multiplies and divides in a single cycle. The FPU

Floating point unit

A floating-point unit is a part of a computer system specially designed to carry out operations on floating point numbers. Typical operations are addition, subtraction, multiplication, division, and square root...

portion of the design was separate from the instruction decoder and integer parts, allowing the decoder to send instructions to both the FPU and ALU

Arithmetic logic unit

In computing, an arithmetic logic unit is a digital circuit that performs arithmetic and logical operations.The ALU is a fundamental building block of the central processing unit of a computer, and even the simplest microprocessors contain one for purposes such as maintaining timers...

(integer) execution unit

Execution unit

In computer engineering, an execution unit is a part of a CPU that performs the operations and calculations called for by the Branch Unit, which receives data from the CPU...

s at the same time. IBM complemented this with a complex instruction decoder which could be fetching one instruction, decoding another, and sending one to the ALU and FPU at the same time, resulting in one of the first superscalar

Superscalar

A superscalar CPU architecture implements a form of parallelism called instruction level parallelism within a single processor. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate...

CPU designs in use.

The system used 32 32-bit integer

Integer

The integers are formed by the natural numbers together with the negatives of the non-zero natural numbers .They are known as Positive and Negative Integers respectively...

register

Processor register

In computer architecture, a processor register is a small amount of storage available as part of a CPU or other digital processor. Such registers are addressed by mechanisms other than main memory and can be accessed more quickly...

s and another 32 64-bit floating point registers, each in their own unit. The branch unit also included a number of "private" registers for its own use, including the program counter

Program counter

The program counter , commonly called the instruction pointer in Intel x86 microprocessors, and sometimes called the instruction address register, or just part of the instruction sequencer in some computers, is a processor register that indicates where the computer is in its instruction sequence...

.

Another interesting feature of the architecture is a virtual address system which maps all addresses into a 52-bit space. In this way applications can share memory in a "flat" 32-bit space, and all of the programs can have different blocks of 32 bits each.

External links

- Linux on Power

- Linux on Power Support

- Linux on Power WIKI

- IBM Power Architecture weekly magazine

- Power.org

- Power-Admin.org

- POWER to the people - an IBM history of POWER and PowerPC

- Migrating Source Programs

- Meet the experts: John McCalpin - interesting discussion on power5 and beyond

- 27 years of IBM RISC