OpenRISC 1200

Encyclopedia

Soft microprocessor

A soft microprocessor is a microprocessor core that can be wholly implemented using logic synthesis...

maintained by developers at OpenCores.org

OpenCores

OpenCores is the world's largest open source hardware community developing digital open source hardware through electronic design automation, with a similar ethos to the free software movement. OpenCores hopes to eliminate redundant design work and slash development costs. A number of companies...

. The OR1200 design is an open source

Open source

The term open source describes practices in production and development that promote access to the end product's source materials. Some consider open source a philosophy, others consider it a pragmatic methodology...

implementation of the OpenRISC

OpenRISC

OpenRISC is the original flagship project of the OpenCores community. This project aims to develop a series of general purpose open source RISC CPU architectures...

1000 RISC architecture http://opencores.org/openrisc,architecture. The Verilog RTL description is released under the GNU Lesser General Public License

GNU Lesser General Public License

The GNU Lesser General Public License or LGPL is a free software license published by the Free Software Foundation . It was designed as a compromise between the strong-copyleft GNU General Public License or GPL and permissive licenses such as the BSD licenses and the MIT License...

(LGPL).

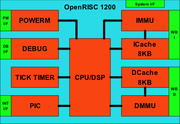

Architecture

The IP core of the OR1200 is implemented in the VerilogVerilog

In the semiconductor and electronic design industry, Verilog is a hardware description language used to model electronic systems. Verilog HDL, not to be confused with VHDL , is most commonly used in the design, verification, and implementation of digital logic chips at the register-transfer level...

HDL

Hardware description language

In electronics, a hardware description language or HDL is any language from a class of computer languages, specification languages, or modeling languages for formal description and design of electronic circuits, and most-commonly, digital logic...

. As an open source core, the design is fully public and may be downloaded and modified by any individual. The official implementation is maintained by developers at OpenCores.org. The implementation specifies a power management unit, debug unit, tick timer, programmable interrupt controller

Programmable Interrupt Controller

In computing, a programmable interrupt controller is a device that is used to combine several sources of interrupt onto one or more CPU lines, while allowing priority levels to be assigned to its interrupt outputs. When the device has multiple interrupt outputs to assert, it will assert them in...

(PIC), central processing unit (CPU), and memory management hardware. Peripheral systems and a memory subsystem may be added using the processor's implementation of a standardized 32-bit Wishbone

Wishbone (computer bus)

The Wishbone Bus is an open source hardware computer bus intended to let the parts of an integrated circuit communicate with each other. The aim is to allow the connection of differing cores to each other inside of a chip...

bus interface. The OR1200 is intended to have a performance comparable to an ARM10

ARM architecture

ARM is a 32-bit reduced instruction set computer instruction set architecture developed by ARM Holdings. It was named the Advanced RISC Machine, and before that, the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit ISA in numbers produced...

processor architecture.

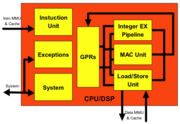

CPU/DSP

The OR1200 CPU is an implementation of the 32-bit ORBIS32 instruction set architecture (ISA) and (optionally) ORFP32X ISA implementing IEEE-754IEEE floating-point standard

IEEE 754–1985 was an industry standard for representingfloating-pointnumbers in computers, officially adopted in 1985 and superseded in 2008 byIEEE 754-2008. During its 23 years, it was the most widely used format for...

compliant single precision floating point support. The ISA has five instruction formats and supports two addressing modes: register indirect with displacement, and PC-relative. The implementation has a single-issue 5-stage pipeline and is capable of single cycle execution on most instructions. The CPU also contains a MAC unit in order to better support digital signal processing

Digital signal processor

A digital signal processor is a specialized microprocessor with an architecture optimized for the fast operational needs of digital signal processing.-Typical characteristics:...

(DSP) applications.

Memory Management

The OR1200 design uses a Harvard memory architectureHarvard architecture

The Harvard architecture is a computer architecture with physically separate storage and signal pathways for instructions and data. The term originated from the Harvard Mark I relay-based computer, which stored instructions on punched tape and data in electro-mechanical counters...

and therefore has separate memory management units (MMUs) for data and instruction memories. These MMUs each consist of a hash-based 1-way direct-mapped translation lookaside buffer

Translation Lookaside Buffer

A translation lookaside buffer is a CPU cache that memory management hardware uses to improve virtual address translation speed. All current desktop and server processors use a TLB to map virtual and physical address spaces, and it is ubiquitous in any hardware which utilizes virtual memory.The...

(TLB) with page size of 8 KB and a default size of 64 entries. The TLBs are individually scalable from 16 to 256 entries. There is also a one-way direct-mapped cache

CPU cache

A CPU cache is a cache used by the central processing unit of a computer to reduce the average time to access memory. The cache is a smaller, faster memory which stores copies of the data from the most frequently used main memory locations...

each for both the instruction memory and for the data memory. Each cache has a default size of 8 KB, but both are individually scalable between 1 and 64 KB. The MMU includes support for virtual memory.

Performance

The core achieves 1.34 CoreMarks per MHz at 50MHz on Xilinx FPGA technology.http://opencores.org/or1k/OR1200_OpenRISC_Processor#Implementation_informationUnder the worst case, the clock cycle for the OR1200 is 250 MHz at a 0.18 µm 6LM fabrication process. Using the Dhrystone

Dhrystone

Dhrystone is a synthetic computing benchmark program developed in 1984 by Reinhold P. Weicker intended to be representative of system programming. The Dhrystone grew to become representative of general processor performance...

benchmark, a 250 MHz OR1200 processor performs 250 Dhrystone millions of instructions per second (DMIPS) in the worst case. Estimated power usage of a 250 MHz processor at a .18µm process is less than 1W at full throttle and less than 5mW at half throttle.

Applications

Generally, the OR1200 is intended to be used in a variety of embedded applications, including telecommunications, portable media, home entertainment, and automotive applications. The GNU toolchainGNU toolchain

The GNU toolchain is a blanket term for a collection of programming tools produced by the GNU Project. These tools form a toolchain used for developing applications and operating systems....

(including GCC

GNU Compiler Collection

The GNU Compiler Collection is a compiler system produced by the GNU Project supporting various programming languages. GCC is a key component of the GNU toolchain...

) has also been successfully ported to the architecture to aid in software development. There is a port of the Linux kernel

Linux kernel

The Linux kernel is an operating system kernel used by the Linux family of Unix-like operating systems. It is one of the most prominent examples of free and open source software....

for OR1K which runs on the OR1200. Recent ports of the embedded C libraries newlib

Newlib

Newlib is a C standard library implementation intended for use on embedded systems. It is a conglomeration of several library parts, all under free software licenses that make them easily usable on embedded products....

and uClibc

UClibc

In computing, uClibc is a small C standard library intended for embedded Linux systems. uClibc was created to support uClinux, a version of Linux not requiring a memory management unit and thus suited for microcontrollers .The project lead is Erik Andersen. The other main contributor is Manuel...

are also available for the platform.

Implementations

The OR1200 has been successfully implemented using FPGAField-programmable gate array

A field-programmable gate array is an integrated circuit designed to be configured by the customer or designer after manufacturing—hence "field-programmable"...

and ASIC

Application-specific integrated circuit

An application-specific integrated circuit is an integrated circuit customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC...

technologies.