VAX 8000

Encyclopedia

The VAX 8000 was a family of minicomputers developed and manufactured by Digital Equipment Corporation

(DEC) using processors implementing the VAX

instruction set architecture (ISA).

The VAX 8600, code-named "Venus", was the successor of the VAX-11/785

The VAX 8600, code-named "Venus", was the successor of the VAX-11/785

introduced in October 1984. It was originally to be named "VAX-11/790", but was renamed before launch. The VAX 8600 was a successful model and at the time was the best selling high-end VAX. It was succeeded by the VAX 8800 family in 1987.

The VAX 8600 had a CPU with an 80 ns cycle time (12.5 MHz) implemented with emitter coupled logic

(ECL) macrocell array

s (MCAs). The CPU consisted of four major logical sections, the E Box, F Box, I Box and M Box. The E Box executed all instructions, including floating-point instructions through microcode. It had an arithmetic logic unit

(ALU) and barrel shifter

. The F Box, or floating point accelerator (FPA), was an optional feature that accelerated floating-point instructions as well as integer multiplication and division. It was a two-module set consisting of an adder module and multiplier module. The adder module contained 24 macrocell arrays while the multiplier module contained 21. The I Box fetched and decoded instructions. The M Box controlled the memory and I/O, translated virtual addresses to physical addresses and contained a 16 KB data cache.

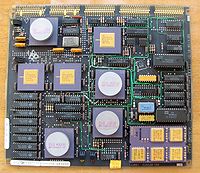

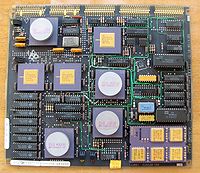

The CPU used 145 MCAs. These were large scale integration devices fabricated by Motorola in their 3 µm MOSAIC bipolar

process. They were packaged in 68-pin leadless chip carriers or pin grid array

s and were mounted onto the printed circuit board in sockets or were soldered in place. An additional 1,100 small scale integration (SSI) and medium scale integration (MSI) ECL logic devices were used. These ICs were spread out over 17 modules plugged into a backplane.

The VAX 8600 supported 4 to 256 MB of ECC

memory and had eight slots on the backplane for memory modules. The system originally used 4 MB memory modules populated by 32 KB metal oxide semiconductor (MOS) RAMs, which limited capacity to 32 MB. Modules with larger capacities were introduced later. The memory was controlled by the M Box, which also provided the memory array bus used to access the memory. This dedicated bus, which had an 80 ns (12.5 MHz) cycle time, contributed to the improved performance the VAX 8600 had over the VAX-11/780, which accessed memory via the Synchronous Backplane Interconnect

(SBI) that was shared with I/O devices.

I/O was provided by the SBI. The VAX 8600 featured one SBI but could be configured with two. The SBIs were provided by SBI adapters that interfaced the SBI to an internal adapter bus connected to the M Box. Each SBI had 16 slots for I/O devices, although only 15 were usable as one slot was reserved for the SBI adapter. With one SBI, that SBI had a bandwidth of 13.3 MB/s. With two SBIs, they had a total bandwidth of 17.1 MB/s. The adapter bus that interfaced the SBIs to the M Box had a bandwidth of 33.3 MB/s. Unibus

and Massbus

were also supported, provided by adapters that plugged into the SBI. The VAX 8600 I/O cabinet contained a PDP-11

computer serving as the console, a Unibus card cage and provisions for mounting disk drives.

and VAX-11/785

, to have the PDP-11

compatibility mode, and to use the SBI also used by the VAX-11/78x. The CPU had a 55 ns cycle time (18.18 MHz).

The VAX 8200 and VAX 8300, code named "Scorpio", were mid-range minicomputers introduced on 29 January 1986. The VAX 8300 was a dual-processor variant of the VAX 8200 and, with the VAX 8800 introduced on the same date, was among the first multiprocessor

The VAX 8200 and VAX 8300, code named "Scorpio", were mid-range minicomputers introduced on 29 January 1986. The VAX 8300 was a dual-processor variant of the VAX 8200 and, with the VAX 8800 introduced on the same date, was among the first multiprocessor

VAX computers. They used the KA820 CPU module containing a V-11

microprocessor operating at 5 MHz (200 ns cycle) and supported a maximum of 128 MB of ECC memory. It had one VAXBI bus and support for an optional Unibus

.

s during operation to limit performance.

(CPU) operated at 22.22 MHz (45 ns cycle time) and was implemented with discrete emitter-coupled logic

(ECL) devices spread over eight modules. The majority of the ECL devices were macrocell array

s with 1,200 logic gate

s, while the general-purpose registers and floating-point units were custom logic devices developed by Digital. The CPU had 64 KB of cache implemented with 10 ns and 15 ns ECL random access memory devices.

The memory system consisted of three major parts, a memory controller

, a transistor-transistor logic

(TTL) bus and one to eight memory array modules. The memory controller was implemented with ECL gate arrays and resided on a NMI bus module. It implemented a TTL bus to which memory array modules were connected. Two memory modules were available for the VAX 8800: a 4 MB module and a 16 MB module. The 4 MB array module was an eight-layer printed circuit board populated by metal oxide semiconductor (MOS) dynamic random access memory

(DRAM) devices and medium-scale integration (MSI) FAST transistor-transistor logic

(TTL) devices in roughly equal numbers. The 16 MB array module was similar to the 4 MB module, but contained eight surface-mounted daughter boards, each containing 2 MB of memory built from DRAMs.

(DMA) transactions to and from the I/O devices. The adapter operated at 5 MHz and asynchronously to the CPU as it generated its own clock signal

. The NBI adapter consisted of two modules, the NBIA and NBIB. The NBIA was the NMI side of the adapter, and the NBIB the VAXBI side.

Digital Equipment Corporation

Digital Equipment Corporation was a major American company in the computer industry and a leading vendor of computer systems, software and peripherals from the 1960s to the 1990s...

(DEC) using processors implementing the VAX

VAX

VAX was an instruction set architecture developed by Digital Equipment Corporation in the mid-1970s. A 32-bit complex instruction set computer ISA, it was designed to extend or replace DEC's various Programmed Data Processor ISAs...

instruction set architecture (ISA).

VAX 8600

VAX-11

The VAX-11 was a family of minicomputers developed and manufactured by Digital Equipment Corporation using processors implementing the VAX instruction set architecture . The VAX-11/780 was the first VAX computer.- VAX-11/780 :...

introduced in October 1984. It was originally to be named "VAX-11/790", but was renamed before launch. The VAX 8600 was a successful model and at the time was the best selling high-end VAX. It was succeeded by the VAX 8800 family in 1987.

The VAX 8600 had a CPU with an 80 ns cycle time (12.5 MHz) implemented with emitter coupled logic

Emitter coupled logic

In electronics, emitter-coupled logic , is a logic family that achieves high speed by using an overdriven BJT differential amplifier with single-ended input, whose emitter current is limited to avoid the slow saturation region of transistor operation....

(ECL) macrocell array

Macrocell array

A macrocell array is an approach to the design and manufacture of ASICs. Essentially, it is a small step up from the otherwise similar gate array, but rather than being a prefabricated array of simple logic gates, the macrocell array is a prefabricated array of higher-level logic functions such as...

s (MCAs). The CPU consisted of four major logical sections, the E Box, F Box, I Box and M Box. The E Box executed all instructions, including floating-point instructions through microcode. It had an arithmetic logic unit

Arithmetic logic unit

In computing, an arithmetic logic unit is a digital circuit that performs arithmetic and logical operations.The ALU is a fundamental building block of the central processing unit of a computer, and even the simplest microprocessors contain one for purposes such as maintaining timers...

(ALU) and barrel shifter

Barrel shifter

A barrel shifter is a digital circuit that can shift a data word by a specified number of bits in one clock cycle. It can be implemented as a sequence of multiplexers , and in such an implementation the output of one mux is connected to the input of the next mux in a way that depends on the shift...

. The F Box, or floating point accelerator (FPA), was an optional feature that accelerated floating-point instructions as well as integer multiplication and division. It was a two-module set consisting of an adder module and multiplier module. The adder module contained 24 macrocell arrays while the multiplier module contained 21. The I Box fetched and decoded instructions. The M Box controlled the memory and I/O, translated virtual addresses to physical addresses and contained a 16 KB data cache.

The CPU used 145 MCAs. These were large scale integration devices fabricated by Motorola in their 3 µm MOSAIC bipolar

Bipolar junction transistor

|- align = "center"| || PNP|- align = "center"| || NPNA bipolar transistor is a three-terminal electronic device constructed of doped semiconductor material and may be used in amplifying or switching applications. Bipolar transistors are so named because their operation involves both electrons...

process. They were packaged in 68-pin leadless chip carriers or pin grid array

Pin grid array

A pin grid array, often abbreviated PGA, is a type of integrated circuit packaging. In a PGA, the package is square or roughly square, and the pins are arranged in a regular array on the underside of the package...

s and were mounted onto the printed circuit board in sockets or were soldered in place. An additional 1,100 small scale integration (SSI) and medium scale integration (MSI) ECL logic devices were used. These ICs were spread out over 17 modules plugged into a backplane.

The VAX 8600 supported 4 to 256 MB of ECC

ECC

-Companies:* ECC , Education through Communication for the Community, a Japanese company* Electric Car Corporation plc, a British adapter and seller of electric cars* English China Clays, an English company-Education:...

memory and had eight slots on the backplane for memory modules. The system originally used 4 MB memory modules populated by 32 KB metal oxide semiconductor (MOS) RAMs, which limited capacity to 32 MB. Modules with larger capacities were introduced later. The memory was controlled by the M Box, which also provided the memory array bus used to access the memory. This dedicated bus, which had an 80 ns (12.5 MHz) cycle time, contributed to the improved performance the VAX 8600 had over the VAX-11/780, which accessed memory via the Synchronous Backplane Interconnect

Synchronous Backplane Interconnect

The Synchronous Backplane Interconnect was the internal processor-memory bus used by early VAX computers manufactured by the Digital Equipment Corporation of Maynard, Massachusetts....

(SBI) that was shared with I/O devices.

I/O was provided by the SBI. The VAX 8600 featured one SBI but could be configured with two. The SBIs were provided by SBI adapters that interfaced the SBI to an internal adapter bus connected to the M Box. Each SBI had 16 slots for I/O devices, although only 15 were usable as one slot was reserved for the SBI adapter. With one SBI, that SBI had a bandwidth of 13.3 MB/s. With two SBIs, they had a total bandwidth of 17.1 MB/s. The adapter bus that interfaced the SBIs to the M Box had a bandwidth of 33.3 MB/s. Unibus

Unibus

The Unibus was the earliest of several computer bus technologies used with PDP-11 and early VAX systems manufactured by the Digital Equipment Corporation of Maynard, Massachusetts.-History:...

and Massbus

Massbus

The Massbus was a high-performance computer input/output bus designed in the 1970s by the Digital Equipment Corporation of Maynard, Massachusetts....

were also supported, provided by adapters that plugged into the SBI. The VAX 8600 I/O cabinet contained a PDP-11

PDP-11

The PDP-11 was a series of 16-bit minicomputers sold by Digital Equipment Corporation from 1970 into the 1990s, one of a succession of products in the PDP series. The PDP-11 replaced the PDP-8 in many real-time applications, although both product lines lived in parallel for more than 10 years...

computer serving as the console, a Unibus card cage and provisions for mounting disk drives.

VAX 8650

The VAX 8650, code-named "Morningstar", was a faster version of the VAX 8600 introduced on 4 December 1985. It was originally to be named "VAX-11/795", but was renamed before launch. The VAX 8600 was the last VAX to be 100% compatible with the VAX-11/780VAX-11

The VAX-11 was a family of minicomputers developed and manufactured by Digital Equipment Corporation using processors implementing the VAX instruction set architecture . The VAX-11/780 was the first VAX computer.- VAX-11/780 :...

and VAX-11/785

VAX-11

The VAX-11 was a family of minicomputers developed and manufactured by Digital Equipment Corporation using processors implementing the VAX instruction set architecture . The VAX-11/780 was the first VAX computer.- VAX-11/780 :...

, to have the PDP-11

PDP-11

The PDP-11 was a series of 16-bit minicomputers sold by Digital Equipment Corporation from 1970 into the 1990s, one of a succession of products in the PDP series. The PDP-11 replaced the PDP-8 in many real-time applications, although both product lines lived in parallel for more than 10 years...

compatibility mode, and to use the SBI also used by the VAX-11/78x. The CPU had a 55 ns cycle time (18.18 MHz).

VAX 8200 and VAX 8300

Multiprocessor

Computer system having two or more processing units each sharing main memory and peripherals, in order to simultaneously process programs.Sometimes the term Multiprocessor is confused with the term Multiprocessing....

VAX computers. They used the KA820 CPU module containing a V-11

V-11

The V-11, code-named "Scorpio", is a microprocessor chip set implementation of the VAX instruction set architecture developed and fabricated by Digital Equipment Corporation .- History :...

microprocessor operating at 5 MHz (200 ns cycle) and supported a maximum of 128 MB of ECC memory. It had one VAXBI bus and support for an optional Unibus

Unibus

The Unibus was the earliest of several computer bus technologies used with PDP-11 and early VAX systems manufactured by the Digital Equipment Corporation of Maynard, Massachusetts.-History:...

.

VAX 8250 and VAX 8350

The VAX 8250 and VAX 8350 were faster models of the VAX 8200 and VAX 8300 introduced in early March 1987. They used the KA825 CPU module containing a V-11 microprocessor operating at 6.25 MHz (160 ns cycle).VAX 8800

Code-named "Nautilus", this was the high-end model in the VAX 8800 family. It featured two CPUs and two VAXBI buses as standard. Development of the VAX 8800 began in August–November 1982 and it was introduced on 29 January 1986. When "Polarstar" systems and a new naming convention were introduced, the VAX 8800 was renamed to VAX 8820N to distinguish it from the VAX 8820 "Polarstar".VAX 8700

The VAX 8700, code-named "Nautilus", was introduced in early August 1986. It was similar to the VAX 8800, but with only one CPU and VAXBI bus. It was upgradable to a VAX 8800.VAX 8550

The VAX 8550, code-named "Skipjack", was introduced in early August 1986. It was similar to the VAX 8700, but was not upgradable to the VAX 8800.VAX 8500

The VAX 8500, code-named "Flounder", was a lower-performance variant of the VAX 8550, with microcode used to insert nopNOP

In computer science, NOP or NOOP is an assembly language instruction, sequence of programming language statements, or computer protocol command that effectively does nothing at all....

s during operation to limit performance.

VAX 8530

The VAX 8530, code-named "Skipjack", was an upgraded VAX 8500 with the nops removed for improved performance. It was introduced in early March 1987.Polarstar

Polarstar was a variant of Nautilus with one to four processors and an updated console processor. Models included the:- VAX 8810 - A single processor system

- VAX 8820 - A two processor system

- VAX 8842 - A cluster of two VAX 8820 systems

- VAX 8830 - A three processor system

- VAX 8840 - A four processor system

- VAX 8974 - Introduced on 20 January 1987, it was a cluster of four VAX 8700 systems

- VAX 8978 - introduced on 20 January 1987, it was a cluster of eight VAX 8700 systems

Description

The VAX 8800 family was based on the NMI bus, which connected the CPU, memory controller and I/O adapters. The NMI bus was a 32-bit synchronous bus with a usable bandwidth of 64 MB/s.CPU

The VAX 8800 family central processing unitCentral processing unit

The central processing unit is the portion of a computer system that carries out the instructions of a computer program, to perform the basic arithmetical, logical, and input/output operations of the system. The CPU plays a role somewhat analogous to the brain in the computer. The term has been in...

(CPU) operated at 22.22 MHz (45 ns cycle time) and was implemented with discrete emitter-coupled logic

Emitter-coupled logic

In electronics, emitter-coupled logic , is a logic family that achieves high speed by using an overdriven BJT differential amplifier with single-ended input, whose emitter current is limited to avoid the slow saturation region of transistor operation....

(ECL) devices spread over eight modules. The majority of the ECL devices were macrocell array

Macrocell array

A macrocell array is an approach to the design and manufacture of ASICs. Essentially, it is a small step up from the otherwise similar gate array, but rather than being a prefabricated array of simple logic gates, the macrocell array is a prefabricated array of higher-level logic functions such as...

s with 1,200 logic gate

Logic gate

A logic gate is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logic inputs and produces a single logic output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and...

s, while the general-purpose registers and floating-point units were custom logic devices developed by Digital. The CPU had 64 KB of cache implemented with 10 ns and 15 ns ECL random access memory devices.

Memory

The VAX 8800 and 8700 supported one to eight memory array modules; the VAX 8550 and 8500, one to five. The memory array modules were installed in a dedicated backplane separate from the NMI backplane. The VAX 8800 and VAX 8700 supported 4 to 32 MB of memory, the VAX 8500 and VAX 8550 4 to 20 MB, using the 4 MB memory module. When the 16 MB memory module was introduced, the memory capacity of the VAX 8800 and 8700 was increased to 128 MB, and that of the VAX 8550 and 8500 to 80 MB.The memory system consisted of three major parts, a memory controller

Memory controller

The memory controller is a digital circuit which manages the flow of data going to and from the main memory. It can be a separate chip or integrated into another chip, such as on the die of a microprocessor...

, a transistor-transistor logic

Transistor-transistor logic

Transistor–transistor logic is a class of digital circuits built from bipolar junction transistors and resistors. It is called transistor–transistor logic because both the logic gating function and the amplifying function are performed by transistors .TTL is notable for being a widespread...

(TTL) bus and one to eight memory array modules. The memory controller was implemented with ECL gate arrays and resided on a NMI bus module. It implemented a TTL bus to which memory array modules were connected. Two memory modules were available for the VAX 8800: a 4 MB module and a 16 MB module. The 4 MB array module was an eight-layer printed circuit board populated by metal oxide semiconductor (MOS) dynamic random access memory

Dynamic random access memory

Dynamic random-access memory is a type of random-access memory that stores each bit of data in a separate capacitor within an integrated circuit. The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1...

(DRAM) devices and medium-scale integration (MSI) FAST transistor-transistor logic

Transistor-transistor logic

Transistor–transistor logic is a class of digital circuits built from bipolar junction transistors and resistors. It is called transistor–transistor logic because both the logic gating function and the amplifying function are performed by transistors .TTL is notable for being a widespread...

(TTL) devices in roughly equal numbers. The 16 MB array module was similar to the 4 MB module, but contained eight surface-mounted daughter boards, each containing 2 MB of memory built from DRAMs.

I/O

The VAX 8800 used the VAXBI bus for input/output. The VAX 8800 supported up to four VAXBI buses, with each bus supporting up to 16 I/O devices. The VAXBI bus was interfaced to the NMI bus by a NBI adapter containing a chip implementing the VAXBI bus protocol. The NBI adapter handled all CPU references and direct memory accessDirect memory access

Direct memory access is a feature of modern computers that allows certain hardware subsystems within the computer to access system memory independently of the central processing unit ....

(DMA) transactions to and from the I/O devices. The adapter operated at 5 MHz and asynchronously to the CPU as it generated its own clock signal

Clock signal

In electronics and especially synchronous digital circuits, a clock signal is a particular type of signal that oscillates between a high and a low state and is utilized like a metronome to coordinate actions of circuits...

. The NBI adapter consisted of two modules, the NBIA and NBIB. The NBIA was the NMI side of the adapter, and the NBIB the VAXBI side.