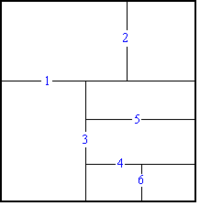

Floorplan (microelectronics)

Encyclopedia

Electronic design automation

Electronic design automation is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits...

, a floorplan of an integrated circuit

Integrated circuit

An integrated circuit or monolithic integrated circuit is an electronic circuit manufactured by the patterned diffusion of trace elements into the surface of a thin substrate of semiconductor material...

is a schematic representation of tentative placement

Placement (EDA)

Placement is an essential step in electronic design automation - the portion of the physical design flow that assigns exact locations for various circuitcomponents within the chip’s core area...

of its major functional blocks.

In modern electronic design process floorplans are created during the floorplanning design stage, an early stage in the hierarchical approach to chip design.

Depending on the design methodology being followed, the actual definition of a floorplan may differ.

Floorplanning

Floorplanning takes in some of the geometrical constraints in a design. Examples of this are:- bonding pads for off-chip connections (often using wire bondingWire bondingWire bonding is the primary method of making interconnections between an integrated circuit and a printed circuit board during semiconductor device fabrication. Although less common, wire bonding can be used to connect an IC to other electronics or to connect from one PCB to another...

) are normally located at the circumference of the chip; - line drivers often have to be located as close to bonding pads as possible;

- chip area is therefore in some cases given a minimum area in order to fit in the required number of pads;

- areas are clustered in order to limit data paths thus frequently featuring defined structures such as cacheCacheIn computer engineering, a cache is a component that transparently stores data so that future requests for that data can be served faster. The data that is stored within a cache might be values that have been computed earlier or duplicates of original values that are stored elsewhere...

RAMRam-Animals:*Ram, an uncastrated male sheep*Ram cichlid, a species of freshwater fish endemic to Colombia and Venezuela-Military:*Battering ram*Ramming, a military tactic in which one vehicle runs into another...

, multiplierMultiplierThe term multiplier may refer to:In electrical engineering:* Binary multiplier, a digital circuit to perform rapid multiplication of two numbers in binary representation* Analog multiplier, a device that multiplies two analog signals...

, barrel shifterBarrel shifterA barrel shifter is a digital circuit that can shift a data word by a specified number of bits in one clock cycle. It can be implemented as a sequence of multiplexers , and in such an implementation the output of one mux is connected to the input of the next mux in a way that depends on the shift...

, line driverLine driverIn electronics, a line driver is an amplifier used to improve the strength of an analog or digital signal at its source by driving the input to the transmission line with a higher than normal signal level. This increases the quality of a transmission over a long run of cable...

and arithmetic logic unitArithmetic logic unitIn computing, an arithmetic logic unit is a digital circuit that performs arithmetic and logical operations.The ALU is a fundamental building block of the central processing unit of a computer, and even the simplest microprocessors contain one for purposes such as maintaining timers...

; - purchased intellectual property blocks (IP-blocks), such as a processor core, come in predefined area blocks;

- some IP-blocks come with legal limitations such as permitting no routing of signals directly above the block.

Mathematical models and optimization problems

In some approaches the floorplan may be a partition of the whole chip area into axis aligned rectangles to be occupied by IC blocks. This partition is subject to various constraints and requirements of optimization: block area, aspect ratioAspect ratio

The aspect ratio of a shape is the ratio of its longer dimension to its shorter dimension. It may be applied to two characteristic dimensions of a three-dimensional shape, such as the ratio of the longest and shortest axis, or for symmetrical objects that are described by just two measurements,...

s, estimated total measure of interconnects, etc.

Finding good floorplans has been a research area in combinatorial optimization

Combinatorial optimization

In applied mathematics and theoretical computer science, combinatorial optimization is a topic that consists of finding an optimal object from a finite set of objects. In many such problems, exhaustive search is not feasible...

. Most of the problems related to finding optimal floorplans are NP-hard

NP-hard

NP-hard , in computational complexity theory, is a class of problems that are, informally, "at least as hard as the hardest problems in NP". A problem H is NP-hard if and only if there is an NP-complete problem L that is polynomial time Turing-reducible to H...

, i.e., require vast computational resources. Therefore, the most common approach is to use various optimization heuristics for finding good solutions.

Another approach is to restrict design methodology to certain classes of floorplans, such as sliceable floorplans.

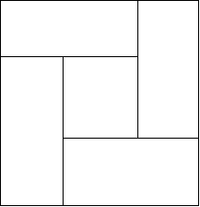

Sliceable floorplans

- A floorplan that consists of a single rectangular block is sliceable.

- If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

Sliceable floorplans have been used in a number of early Electronic Design Automation

Electronic design automation

Electronic design automation is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits...

tools for a number of reasons. Sliceable floorplans may be conveniently represented by binary tree

Binary tree

In computer science, a binary tree is a tree data structure in which each node has at most two child nodes, usually distinguished as "left" and "right". Nodes with children are parent nodes, and child nodes may contain references to their parents. Outside the tree, there is often a reference to...

s which correspond to the order of slicing. More importantly, a number of NP-hard problems with floorplans have polynomial time algorithms when restricted to sliceable floorplans.