P5 (microarchitecture)

Encyclopedia

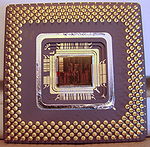

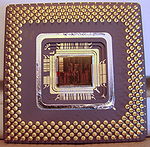

The original Pentium microprocessor

was introduced on March 22, 1993. Its microarchitecture

, deemed P5, was Intel's fifth-generation and first superscalar

x86 microarchitecture

. As a direct extension of the 80486 architecture, it included dual integer

pipelines, a faster FPU

, wider data bus, separate code and data caches and features for further reduced address calculation latency. In 1996, the Pentium with MMX Technology (often simply referred to as Pentium MMX) was introduced with the same basic microarchitecture complemented with an MMX instruction set, larger caches, and some other enhancements.

The P5 Pentium competitors included the Motorola 68060

and the PowerPC 601 as well as the SPARC

, MIPS

, and Alpha

microprocessor families, most of which also used a superscalar in-order dual instruction pipeline configuration at some time.

Intel's Larrabee multicore architecture project uses a processor core derived from a P5 core (P54C), augmented by multithreading, 64-bit instructions, and a 16-wide vector processing unit. Intel's low-powered Bonnell microarchitecture employed in Atom

processor cores also uses an in-order dual pipeline similar to P5.

architecture, with on-chip cache, floating-point, and branch prediction. The preliminary design was first successfully simulated in 1990, followed by the laying-out

of the design. By this time the team had several dozen engineers. The design was taped out

, or transferred to silicon, in April 1992, at which point beta-testing began. By mid-1992, the P5 team had 200 engineers. Intel at first planned to demonstrate the P5 in June 1992 at the trade show PC Expo, and to formally announce the processor in September 1992, but design problems forced the demo to be cancelled, and the official introduction of the chip was delayed until the spring of 1993.

John H. Crawford, chief architect of the original 386, co-managed the design of the P5, along with Donald Alpert, who managed the architectural team. Dror Avnon managed the design of the FPU. Vinod K. Dham was general manager of the P5 group.

The Pentium was designed to execute over 100 million instructions per second

(MIPS), and the 75 MHz model was able to reach 126.5 MIPS in certain benchmarks. The Pentium architecture typically offered just under twice the performance of a 486 processor per clock cycle in common benchmarks. The fastest 80486 parts (with slightly improved microarchitecture and 100 MHz operation) were almost as powerful as the first-generation Pentiums, and the AMD Am5x86 was roughly equal to the Pentium 75 regarding pure ALU performance.

and caused embarrassment for Intel, which created an exchange program to replace the faulty processors. Soon afterwards, a bug was discovered which could allow a malicious program to crash a system without any special privileges (the "f00f" bug); fortunately, operating systems were able to implement workarounds to prevent crashes.

The 60 and 66 MHz 0.8 µm

versions of the P5 Pentium processors also had (for the time) high heat production due to their 5V operation, and were often known colloquially as "coffee warmers" or some similar nickname. The P54C used 3.3V and had significantly lower power draw (a quadratic relationship). P5 Pentiums used Socket 4

, while P54C started out on Socket 5

before moving to Socket 7

in later revisions. All desktop Pentiums from P54CS onwards used Socket 7

.

The first Pentium microprocessor core was code-named "P5". Its product code was 80501 (80500 for the earliest steppings). There were two versions, specified to operate at 60 MHz and 66 MHz respectively. This first implementation of the Pentium used a traditional 5 Volt power supply (descended from the usual TTL logic

The first Pentium microprocessor core was code-named "P5". Its product code was 80501 (80500 for the earliest steppings). There were two versions, specified to operate at 60 MHz and 66 MHz respectively. This first implementation of the Pentium used a traditional 5 Volt power supply (descended from the usual TTL logic

compatibility requirements). It contained 3.1 million transistors and measured 16.7 mm by 17.6 mm for an area of 293.92 mm2. It was fabricated in a 0.8 µm

BiCMOS

process. The 5 volt design resulted in relatively high energy consumption for its operating frequency compared to the later models.

due to differing definitions.

, which only allows connections along the edges of the chip. A smaller chip would have required a redesign of the package, as there is a limit on the length of the wires and the edges of the chip would be further away from the pads on the package. The solution was to keep the chip the same size, retain the existing pad-ring, and only reduce the size of the Pentium's logic circuitry to enable it to achieve higher clock frequencies.

for 486

-systems were released in 1995, which were based on 3.3V 0.6 µm versions using a 63 or 83 MHz clock. Since these used Socket 2

/3

, some modifications had to be made to compensate for the 32-bit data bus and slower on-board L2 cache of 486

-motherboards. They were therefore equipped with a 32KB

L1 cache (double that of pre-P55C Pentium CPUs).

The P55C (or 80503) was developed by Intel's Research & Development Center in Haifa, Israel. It was sold as Pentium with MMX Technology (usually just called Pentium MMX); although it was based on the P5 core, it featured a new set of 57 "MMX" instructions intended to improve performance on multimedia tasks, such as encoding and decoding digital media data. The Pentium MMX line was introduced on 22 October 1996.

The P55C (or 80503) was developed by Intel's Research & Development Center in Haifa, Israel. It was sold as Pentium with MMX Technology (usually just called Pentium MMX); although it was based on the P5 core, it featured a new set of 57 "MMX" instructions intended to improve performance on multimedia tasks, such as encoding and decoding digital media data. The Pentium MMX line was introduced on 22 October 1996.

The new instructions work on new data types: 64-bit packed vectors of either eight 8-bit integers, four 16-bit integers, two 32-bit integers, or one 64-bit integer. So, for example, the PADDUSB (Packed ADD Unsigned Saturated Byte) instruction adds two vectors, each containing eight 8-bit unsigned integers together, pairwise; each addition that would overflow

saturates, yielding 255, the maximum unsigned value that can be represented in a byte. These rather specialized instructions generally require special coding by the programmer for them to be used. The performance of the P55C was improved over previous versions by a doubling of the Level 1 CPU cache

from 16 KB to 32 KB.

It contained 4.5 million transistors and had an area of 140 mm2. It was fabricated in a 0.28 µm CMOS process with the same metal pitches as the previous 0.35 µm BiCMOS process, so Intel described it as "0.35 µm" because of its similar transistor density. The process has four levels of interconnect.

While the P55C is compatible with the common Socket 7

motherboard configuration, the voltage requirements for powering the chip differ from the standard Socket 7 specifications. Most motherboards manufactured for Socket 7 prior to the establishment of the P55C standard are not compliant with the dual intensity required for proper operation of this chip. Intel temporarily manufactured an upgrade kit called the OverDrive that was designed to correct this lack of planning on the motherboard makers part.

with the CPU directly attached to it in a smaller form factor. The module snapped to the notebook motherboard and typically a heat spreader

was installed and made contact with the module. However, with the 0.25 µm Tillamook Mobile Pentium MMX (named after a city in Oregon

), the module also held the 430TX chipset along with the system's 512 KB SRAM

cache memory.

Microprocessor

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit, or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and...

was introduced on March 22, 1993. Its microarchitecture

Microarchitecture

In computer engineering, microarchitecture , also called computer organization, is the way a given instruction set architecture is implemented on a processor. A given ISA may be implemented with different microarchitectures. Implementations might vary due to different goals of a given design or...

, deemed P5, was Intel's fifth-generation and first superscalar

Superscalar

A superscalar CPU architecture implements a form of parallelism called instruction level parallelism within a single processor. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate...

x86 microarchitecture

Microarchitecture

In computer engineering, microarchitecture , also called computer organization, is the way a given instruction set architecture is implemented on a processor. A given ISA may be implemented with different microarchitectures. Implementations might vary due to different goals of a given design or...

. As a direct extension of the 80486 architecture, it included dual integer

Integer

The integers are formed by the natural numbers together with the negatives of the non-zero natural numbers .They are known as Positive and Negative Integers respectively...

pipelines, a faster FPU

Floating point unit

A floating-point unit is a part of a computer system specially designed to carry out operations on floating point numbers. Typical operations are addition, subtraction, multiplication, division, and square root...

, wider data bus, separate code and data caches and features for further reduced address calculation latency. In 1996, the Pentium with MMX Technology (often simply referred to as Pentium MMX) was introduced with the same basic microarchitecture complemented with an MMX instruction set, larger caches, and some other enhancements.

The P5 Pentium competitors included the Motorola 68060

Motorola 68060

The Motorola 68060 is a 32-bit microprocessor from Motorola released in 1994. It is the successor to the Motorola 68040 and is the highest performing member of the 680x0 family. Two derivatives were produced, the 68LC060 and the 68EC060....

and the PowerPC 601 as well as the SPARC

SPARC

SPARC is a RISC instruction set architecture developed by Sun Microsystems and introduced in mid-1987....

, MIPS

MIPS architecture

MIPS is a reduced instruction set computer instruction set architecture developed by MIPS Technologies . The early MIPS architectures were 32-bit, and later versions were 64-bit...

, and Alpha

DEC Alpha

Alpha, originally known as Alpha AXP, is a 64-bit reduced instruction set computer instruction set architecture developed by Digital Equipment Corporation , designed to replace the 32-bit VAX complex instruction set computer ISA and its implementations. Alpha was implemented in microprocessors...

microprocessor families, most of which also used a superscalar in-order dual instruction pipeline configuration at some time.

Intel's Larrabee multicore architecture project uses a processor core derived from a P5 core (P54C), augmented by multithreading, 64-bit instructions, and a 16-wide vector processing unit. Intel's low-powered Bonnell microarchitecture employed in Atom

Intel Atom

Intel Atom is the brand name for a line of ultra-low-voltage x86 and x86-64 CPUs from Intel, designed in 45 nm CMOS and used mainly in netbooks, nettops, embedded application ranging from health care to advanced robotics and Mobile Internet devices...

processor cores also uses an in-order dual pipeline similar to P5.

Development

The P5 microarchitecture was designed by the same Santa Clara team which designed the 386 and 486. Design work started in 1989; the team decided to use a superscalarSuperscalar

A superscalar CPU architecture implements a form of parallelism called instruction level parallelism within a single processor. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate...

architecture, with on-chip cache, floating-point, and branch prediction. The preliminary design was first successfully simulated in 1990, followed by the laying-out

Integrated circuit layout

Integrated circuit layout, also known IC layout, IC mask layout, or mask design, is the representation of an integrated circuit in terms of planar geometric shapes which correspond to the patterns of metal, oxide, or semiconductor layers that make up the components of the integrated circuit.When...

of the design. By this time the team had several dozen engineers. The design was taped out

Tape-out

In electronics design, tape-out or tapeout is the final result of the design cycle for integrated circuits or printed circuit boards, the point at which the artwork for the photomask of a circuit is sent for manufacture....

, or transferred to silicon, in April 1992, at which point beta-testing began. By mid-1992, the P5 team had 200 engineers. Intel at first planned to demonstrate the P5 in June 1992 at the trade show PC Expo, and to formally announce the processor in September 1992, but design problems forced the demo to be cancelled, and the official introduction of the chip was delayed until the spring of 1993.

John H. Crawford, chief architect of the original 386, co-managed the design of the P5, along with Donald Alpert, who managed the architectural team. Dror Avnon managed the design of the FPU. Vinod K. Dham was general manager of the P5 group.

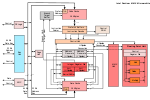

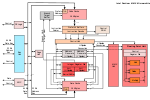

Major improvements over i486 microarchitecture

- Performance:

- SuperscalarSuperscalarA superscalar CPU architecture implements a form of parallelism called instruction level parallelism within a single processor. It therefore allows faster CPU throughput than would otherwise be possible at a given clock rate...

architecture — The Pentium has two datapaths (pipelines) that allow it to complete two instructions per clock cycle in many cases. The main pipe (U) can handle any instruction, while the other (V) can handle the most common simple instructions. Some RISC proponents had argued that the "complicated" x86 instruction set would probably never be implemented by a tightly pipelined microarchitectureMicroarchitectureIn computer engineering, microarchitecture , also called computer organization, is the way a given instruction set architecture is implemented on a processor. A given ISA may be implemented with different microarchitectures. Implementations might vary due to different goals of a given design or...

, much less by a dual pipeline design. The 486 and the Pentium demonstrated that this was indeed possible and feasible. - 64-bit64-bit64-bit is a word size that defines certain classes of computer architecture, buses, memory and CPUs, and by extension the software that runs on them. 64-bit CPUs have existed in supercomputers since the 1970s and in RISC-based workstations and servers since the early 1990s...

external databus doubles the amount of information possible to read or write on each memory access and therefore allows the Pentium to load its code cache faster than the 80486; it also allows faster access and storage of 64-bit and 80-bit x87X87x87 is a floating point-related subset of the x86 architecture instruction set. It originated as an extension of the 8086 instruction set in the form of optional floating point coprocessors that worked in tandem with corresponding x86 CPUs. These microchips had names ending in "87"...

FPU data. - Separation of code and data caches lessens the fetch and operand read/write conflicts compared to the 486. In order to reduce access time and implementation cost, both of them are 2-way associative, instead of the single 4-way cache of the 486. A related enhancement in the Pentium is the ability to read a contiguous block from the code cache even when it is split between two cache lines (at least 17 bytes in worst case).

- Much faster floating pointFloating pointIn computing, floating point describes a method of representing real numbers in a way that can support a wide range of values. Numbers are, in general, represented approximately to a fixed number of significant digits and scaled using an exponent. The base for the scaling is normally 2, 10 or 16...

unit. Some instructions showed an enormous improvement, most notably FMUL, with up to 15 times higher throughput than in the 80486 FPU. The Pentium is also able to execute a FXCH ST(x) instruction in parallel with an ordinary (arithmetical or load/store) FPU instruction. - Four-input address-adders enables the Pentium to further reduce the address calculation latency compared to the 80486. The Pentium can calculate full addressing modes with segment-base + base-register + scaled register + immediate offset in a single cycle; the 486 has a three-input address-adder only, and must therefore divide such calculations between two cycles.

- The microcodeMicrocodeMicrocode is a layer of hardware-level instructions and/or data structures involved in the implementation of higher level machine code instructions in many computers and other processors; it resides in special high-speed memory and translates machine instructions into sequences of detailed...

can employ both pipelines in order to enable auto-repeating instructions such as rep movsw perform one iteration every clock cycle, while the 80486 needed three clocks per iteration (and the earliest x86-chips significantly more than the 486). Also, optimization of the access to the first microcode words during the decode stages helps in making several frequent instructions execute significantly more quickly, especially in their most common forms, and in typical cases. Some examples are (486→Pentium, in clock cycles): CALL (3→1), RET (5→2), shifts/rotates (2~3→1), etc. - A faster, fully hardware-based multiplier makes instructions such as MUL and IMUL several times as fast (and more predictable) than in the 80486; the execution time is reduced from 13~42 clock cycles down to 10~11 for 32-bit operands.

- Virtualized interrupt to speed up virtual 8086 modeVirtual 8086 modeIn the 80386 microprocessor and later, virtual 8086 mode allows the execution of real mode applications that are incapable of running directly in protected mode while the processor is running a protected mode operating system.VM86 mode uses a segmentation scheme identical to that of real mode In...

.

- Superscalar

- Other features:

- Enhanced debug features with the introduction of the Processor-based debug port (See Pentium Processor Debugging in the Developers Manual, Vol 1).

- Enhanced self test features like the L1 cache parity check (see Cache Structure in the Developers Manual, Vol 1).

- The later Pentium MMX also added the MMX instruction set, a basic integer SIMDSIMDSingle instruction, multiple data , is a class of parallel computers in Flynn's taxonomy. It describes computers with multiple processing elements that perform the same operation on multiple data simultaneously...

instruction set extension marketed for use in multimediaMultimediaMultimedia is media and content that uses a combination of different content forms. The term can be used as a noun or as an adjective describing a medium as having multiple content forms. The term is used in contrast to media which use only rudimentary computer display such as text-only, or...

applications. MMX could not be used simultaneously with the x87X87x87 is a floating point-related subset of the x86 architecture instruction set. It originated as an extension of the 8086 instruction set in the form of optional floating point coprocessors that worked in tandem with corresponding x86 CPUs. These microchips had names ending in "87"...

FPU instructions because the registers were reused (to allow for fast context switches). More important enhancements were the doubling of the instruction and data cache sizes and a few microarchitectural changes for better performance.

The Pentium was designed to execute over 100 million instructions per second

Instructions per second

Instructions per second is a measure of a computer's processor speed. Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few branches, whereas realistic workloads typically lead to significantly lower IPS values...

(MIPS), and the 75 MHz model was able to reach 126.5 MIPS in certain benchmarks. The Pentium architecture typically offered just under twice the performance of a 486 processor per clock cycle in common benchmarks. The fastest 80486 parts (with slightly improved microarchitecture and 100 MHz operation) were almost as powerful as the first-generation Pentiums, and the AMD Am5x86 was roughly equal to the Pentium 75 regarding pure ALU performance.

Bugs and problems

The early versions of 60-100 MHz P5 Pentiums had a problem in the floating point unit that resulted in incorrect (but predictable) results from some division operations. This bug, discovered in 1994 by professor Thomas Nicely at Lynchburg College, Virginia, became known as the Pentium FDIV bugPentium FDIV bug

The Pentium FDIV bug was a bug in the Intel P5 Pentium floating point unit . Certain floating point division operations performed with these processors would produce incorrect results...

and caused embarrassment for Intel, which created an exchange program to replace the faulty processors. Soon afterwards, a bug was discovered which could allow a malicious program to crash a system without any special privileges (the "f00f" bug); fortunately, operating systems were able to implement workarounds to prevent crashes.

The 60 and 66 MHz 0.8 µm

Micrometre

A micrometer , is by definition 1×10-6 of a meter .In plain English, it means one-millionth of a meter . Its unit symbol in the International System of Units is μm...

versions of the P5 Pentium processors also had (for the time) high heat production due to their 5V operation, and were often known colloquially as "coffee warmers" or some similar nickname. The P54C used 3.3V and had significantly lower power draw (a quadratic relationship). P5 Pentiums used Socket 4

Socket 4

Socket 4, presented in 1993, was the first CPU socket designed for the early P5 Pentium microprocessors. Socket 4 was the only 5-volt socket for the Pentium. After Socket 4, Intel switched to the 3.3-volt-powered Socket 5. Socket 4 does support a special Pentium OverDrive, which allows running at...

, while P54C started out on Socket 5

Socket 5

Socket 5 was created for the second generation of Intel P5 Pentium processors operating at speeds from 75 to 120 MHz as well as certain Pentium OverDrive and Pentium MMX processors with core voltage 3.3 V. Consisting of 320 pins, this was the first socket to use a staggered pin grid array, or...

before moving to Socket 7

Socket 7

Socket 7 is a physical and electrical specification for an x86-style CPU socket on a personal computer motherboard. The socket supersedes the earlier Socket 5, and accepts P5 Pentium microprocessors manufactured by Intel, as well as compatibles made by Cyrix/IBM, AMD, IDT and others.Socket 7 was...

in later revisions. All desktop Pentiums from P54CS onwards used Socket 7

Socket 7

Socket 7 is a physical and electrical specification for an x86-style CPU socket on a personal computer motherboard. The socket supersedes the earlier Socket 5, and accepts P5 Pentium microprocessors manufactured by Intel, as well as compatibles made by Cyrix/IBM, AMD, IDT and others.Socket 7 was...

.

Cores and steppings

The Pentium was Intel's primary microprocessor for personal computers during the mid-1990s. The original design was reimplemented in newer processes and new features were added to maintain its competitiveness as well as to address specific markets such as portable computers. As a result, there were several variants of the P5 microarchitecture.P5

Transistor-transistor logic

Transistor–transistor logic is a class of digital circuits built from bipolar junction transistors and resistors. It is called transistor–transistor logic because both the logic gating function and the amplifying function are performed by transistors .TTL is notable for being a widespread...

compatibility requirements). It contained 3.1 million transistors and measured 16.7 mm by 17.6 mm for an area of 293.92 mm2. It was fabricated in a 0.8 µm

800 nanometer

The 800 nm process refers to the level of semiconductor process technology that was reached in the 1989–1990 timeframe, by most leading semiconductor companies, like Intel and IBM.-Products featuring 0.8 µm manufacturing process:...

BiCMOS

BiCMOS

BiCMOS is an evolved semiconductor technology that integrates two formerly separate semiconductor technologies - those of the analog bipolar junction transistor and the digital CMOS transistor - in a single integrated circuit device....

process. The 5 volt design resulted in relatively high energy consumption for its operating frequency compared to the later models.

P54C

The P5 was followed by the P54C (80502); there were versions specified to operate at 75, 90, or 100 MHz using a 3.3 volt power supply. This was the first Pentium processor to operate at a 3.3 volts, reducing energy consumption. It employed an internal clock multiplier to let the internal circuitry work at a higher frequency than the external address and data buses, as it is more complicated and cumbersome to increase the external frequency, due to physical constraints. It also allowed two-way multiprocessing and had new power management features as well as an on chip 8259-compatible interrupt controller. It contained 3.3 million transistors and measured 163 mm2. It was fabricated in a BiCMOS process which has been described as both 0.5 µm and 0.6 µm600 nanometer

The 600 nm process refers to the level of semiconductor process technology that was reached in the 1994–1995 timeframe, by most leading semiconductor companies, like Intel and IBM.-Products featuring 0.6 µm manufacturing process:...

due to differing definitions.

P54CQS

The P54C was followed by the P54CQS which operated at 120 MHz. It was fabricated in a 0.35 µm BiCMOS process and was the first commercial microprocessor to be fabricated in a 0.35 µm process. Its transistor count is identical to the P54C and, despite the newer process, it had an identical die area as well. The chip was connected to the package using wire bondingWire bonding

Wire bonding is the primary method of making interconnections between an integrated circuit and a printed circuit board during semiconductor device fabrication. Although less common, wire bonding can be used to connect an IC to other electronics or to connect from one PCB to another...

, which only allows connections along the edges of the chip. A smaller chip would have required a redesign of the package, as there is a limit on the length of the wires and the edges of the chip would be further away from the pads on the package. The solution was to keep the chip the same size, retain the existing pad-ring, and only reduce the size of the Pentium's logic circuitry to enable it to achieve higher clock frequencies.

P54CS

The P54CQS was followed by the P54CS, which operated at 133, 150, 166 and 200 MHz. It contained 3.3 million transistors, measured 90 mm2 and was fabricated in a 0.35 µm BiCMOS process with four levels of interconnect.P24T

The P24T Pentium OverDrivePentium OverDrive

The Pentium OverDrive was a microprocessor marketing brand name used by Intel, to cover a variety of consumer upgrade products sold in the mid 1990s. It was originally released for 486 motherboards, and later some Pentium sockets...

for 486

Intel 80486

The Intel 80486 microprocessor was a higher performance follow up on the Intel 80386. Introduced in 1989, it was the first tightly pipelined x86 design as well as the first x86 chip to use more than a million transistors, due to a large on-chip cache and an integrated floating point unit...

-systems were released in 1995, which were based on 3.3V 0.6 µm versions using a 63 or 83 MHz clock. Since these used Socket 2

Socket 2

Socket 2 was one of the series of CPU sockets into which various x86 microprocessors were inserted. It was an updated Socket 1 with added support for Pentium OverDrive processors....

/3

Socket 3

Socket 3 was one of the series of CPU Sockets into which various x86 microprocessors were inserted. It was sometimes found alongside a secondary socket designed for a math coprocessor chip, in this case the 487. Socket 3 resulted from Intel's creation of lower voltage microprocessors...

, some modifications had to be made to compensate for the 32-bit data bus and slower on-board L2 cache of 486

Intel 80486

The Intel 80486 microprocessor was a higher performance follow up on the Intel 80386. Introduced in 1989, it was the first tightly pipelined x86 design as well as the first x86 chip to use more than a million transistors, due to a large on-chip cache and an integrated floating point unit...

-motherboards. They were therefore equipped with a 32KB

Kilobyte

The kilobyte is a multiple of the unit byte for digital information. Although the prefix kilo- means 1000, the term kilobyte and symbol KB have historically been used to refer to either 1024 bytes or 1000 bytes, dependent upon context, in the fields of computer science and information...

L1 cache (double that of pre-P55C Pentium CPUs).

P55C

The new instructions work on new data types: 64-bit packed vectors of either eight 8-bit integers, four 16-bit integers, two 32-bit integers, or one 64-bit integer. So, for example, the PADDUSB (Packed ADD Unsigned Saturated Byte) instruction adds two vectors, each containing eight 8-bit unsigned integers together, pairwise; each addition that would overflow

Arithmetic overflow

The term arithmetic overflow or simply overflow has the following meanings.# In a computer, the condition that occurs when a calculation produces a result that is greater in magnitude than that which a given register or storage location can store or represent.# In a computer, the amount by which a...

saturates, yielding 255, the maximum unsigned value that can be represented in a byte. These rather specialized instructions generally require special coding by the programmer for them to be used. The performance of the P55C was improved over previous versions by a doubling of the Level 1 CPU cache

CPU cache

A CPU cache is a cache used by the central processing unit of a computer to reduce the average time to access memory. The cache is a smaller, faster memory which stores copies of the data from the most frequently used main memory locations...

from 16 KB to 32 KB.

It contained 4.5 million transistors and had an area of 140 mm2. It was fabricated in a 0.28 µm CMOS process with the same metal pitches as the previous 0.35 µm BiCMOS process, so Intel described it as "0.35 µm" because of its similar transistor density. The process has four levels of interconnect.

While the P55C is compatible with the common Socket 7

Socket 7

Socket 7 is a physical and electrical specification for an x86-style CPU socket on a personal computer motherboard. The socket supersedes the earlier Socket 5, and accepts P5 Pentium microprocessors manufactured by Intel, as well as compatibles made by Cyrix/IBM, AMD, IDT and others.Socket 7 was...

motherboard configuration, the voltage requirements for powering the chip differ from the standard Socket 7 specifications. Most motherboards manufactured for Socket 7 prior to the establishment of the P55C standard are not compliant with the dual intensity required for proper operation of this chip. Intel temporarily manufactured an upgrade kit called the OverDrive that was designed to correct this lack of planning on the motherboard makers part.

Tillamook

Pentium MMX notebook CPUs used a "mobile module" that held the CPU. This module was a PCBPrinted circuit board

A printed circuit board, or PCB, is used to mechanically support and electrically connect electronic components using conductive pathways, tracks or signal traces etched from copper sheets laminated onto a non-conductive substrate. It is also referred to as printed wiring board or etched wiring...

with the CPU directly attached to it in a smaller form factor. The module snapped to the notebook motherboard and typically a heat spreader

Heat spreader

A heat spreader is most often simply a copper plate, having high thermal conductivity. Functionally, it is a heat exchanger that moves heat between a heat source and a secondary heat exchanger whose surface area and geometry are more favorable. By definition, the heat is "spread out", such that...

was installed and made contact with the module. However, with the 0.25 µm Tillamook Mobile Pentium MMX (named after a city in Oregon

Tillamook, Oregon

The city of Tillamook is the county seat of Tillamook County, Oregon, United States. The city is located on the southeast end of Tillamook Bay on the Pacific Ocean. The population was 4,352 at the 2000 census...

), the module also held the 430TX chipset along with the system's 512 KB SRAM

Static random access memory

Static random-access memory is a type of semiconductor memory where the word static indicates that, unlike dynamic RAM , it does not need to be periodically refreshed, as SRAM uses bistable latching circuitry to store each bit...

cache memory.

Models and variants

|

|

|

|

|

|

|

|

|

||||||||||||

| Code name | P5 | P54C | P54CS | P55C | Tillamook | |||||||||||||||

| Product code | 80500/ 80501 | 80502 | 80503 | |||||||||||||||||

| Process size (µm Micrometre A micrometer , is by definition 1×10-6 of a meter .In plain English, it means one-millionth of a meter . Its unit symbol in the International System of Units is μm... ) |

0.80 | 0.60 or 0.35* | 0.35 | 0.35 (later 0.28) | 0.25 | |||||||||||||||

| Socket | Socket 4 | Socket 5/7 | Socket 7 | |||||||||||||||||

| Package | CPGA | CPGA/TCP* | CPGA/PPGA Pin grid array A pin grid array, often abbreviated PGA, is a type of integrated circuit packaging. In a PGA, the package is square or roughly square, and the pins are arranged in a regular array on the underside of the package... /TCP* |

CPGA/PPGA/TCP* | TCP/TCP on MMC-1 MMC-1 Mobile Module Connector 1 , is a 280-pin microprocessor cartridge developed by Intel for used by their mobile Pentium, Pentium MMX, Pentium II and Celeron processors... |

|||||||||||||||

| Clock speed (MHz) | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 120* | 133* | 150* | 166 | 200 | 233 | 200 | 233 | 266 | 300 |

| Bus speed (MHz) | 60 | 66 | 50 | 60 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | |||||||

| Voltage | 5.0 | 5.0 | 3.3 2,9* | 3.3 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 | 3.3 | 2.8 | 2.45 | 2.45 | 2.8 | 2.8 | 2.8 | 1.8 | 1.8 | 2.0 | 2.0 |

| Introduced | 1993-03-22 | 1994-10-10 | 1994-03-07 | 1995-03-27 | 1995-06-12 | 1996-01-04 | 1996-06-10 | 1995-03-27 - 1995-11-01 | 1997-01-08 | 1997-06-02 | 1997-08 | 1998-01 | 1999-01 | |||||||

| An asterisk indicates that these were only available as Mobile Pentium or Mobile Pentium MMX chips for laptop Laptop A laptop, also called a notebook, is a personal computer for mobile use. A laptop integrates most of the typical components of a desktop computer, including a display, a keyboard, a pointing device and speakers into a single unit... s. |

||||||||||||||||||||

|

|||||||

| Code name | P54CTB | ||||||

| Product code | PODPMT60X150 | PODPMT66X166 | PODPMT60X180 | PODPMT66X200 | |||

| Process size (µm) | 0.35 | ||||||

| Socket | Socket 5/7 | ||||||

| Package | CPGA with heatsink, fan and voltage regulator | ||||||

| Clock speed (MHz) | 125 | 150 | 166 | 150 | 180 | 200 | |

| Bus speed (MHz) | 50 | 60 | 66 | 50 | 60 | 66 | |

| Upgrade for | Pentium 75 | Pentium 90 | Pentium 100 and 133 | Pentium 75 | Pentium 90, 120 and 150 | Pentium 100, 133 and 166 | |

| TDP Thermal Design Power The thermal design power , sometimes called thermal design point, refers to the maximum amount of power the cooling system in a computer is required to dissipate. For example, a laptop's CPU cooling system may be designed for a 20 watt TDP, which means that it can dissipate up to 20 watts of heat... (max. W) |

15.6 | 15.6 | 15.6 | 18 | |||

| Voltage | 3.3 | 3.3 | 3.3 | 3.3 | |||

|

|

||||||

| Code name | P55C | Tillamook | |||||

| Product code | FV8050366200 | FV8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT | FV80503CSM66266 | GC80503CSM66266 |

| Process size (µm Micrometre A micrometer , is by definition 1×10-6 of a meter .In plain English, it means one-millionth of a meter . Its unit symbol in the International System of Units is μm... ) |

0.35 | 0.25 | |||||

| Clock speed (MHz) | 200 | 233 | 166 | 166 | 166 | 266 | 266 |

| Bus speed (MHz) | 66 | 66 | 66 | 66 | 66 | 66 | 66 |

| Package | PPGA Pin grid array A pin grid array, often abbreviated PGA, is a type of integrated circuit packaging. In a PGA, the package is square or roughly square, and the pins are arranged in a regular array on the underside of the package... |

PPGA | PPGA | BGA Ball grid array A ball grid array is a type of surface-mount packaging used for integrated circuits.- Description :The BGA is descended from the pin grid array , which is a package with one face covered with pins in a grid pattern. These pins conduct electrical signals from the integrated circuit to the printed... |

BGA | PPGA | BGA |

| TDP Thermal Design Power The thermal design power , sometimes called thermal design point, refers to the maximum amount of power the cooling system in a computer is required to dissipate. For example, a laptop's CPU cooling system may be designed for a 20 watt TDP, which means that it can dissipate up to 20 watts of heat... (max. W) |

15.7 | 17 | 4.5 | 4.1 | 4.1 | 7.6 | 7.6 |

| Voltage | 2.8 | 2.8 | 1.9 | 1.8 | 1.8 | 1.9 | 2.0 |

See also

- CPU designCPU designCPU design is the design engineering task of creating a central processing unit , a component of computer hardware. It is a subfield of electronics engineering and computer engineering.- Overview :CPU design focuses on these areas:...

- COAStCache on a stickCOASt, an acronym for cache on a stick, is a packaging standard for modules containing SRAM used as an L2 cache in a computer. COASt modules look like somewhat over-sized SIMM modules. These modules were somewhat popular in the Apple and PC platforms during early to mid-1990s, but with newer...

(Cache On A Stick), L2 cache modules for Pentium - IA-32IA-32IA-32 , also known as x86-32, i386 or x86, is the CISC instruction-set architecture of Intel's most commercially successful microprocessors, and was first implemented in the Intel 80386 as a 32-bit extension of x86 architecture...

instruction set architecture (ISA) - Pentium compatible processorPentium compatible processorA Pentium compatible processor is a 32-bit processor computer chip which supports the instructions in the IA-32 instruction set that were implemented by the Intel P5 Pentium processor family...

Competitors

- AMD K5AMD K5The K5 was AMD's first x86 processor to be developed entirely in-house. Introduced in March 1996, its primary competition was Intel's Pentium microprocessor. The K5 was an ambitious design, closer to a Pentium Pro than a Pentium regarding technical solutions and internal architecture...

, AMD K6AMD K6The K6 microprocessor was launched by AMD in 1997. The main advantage of this particular microprocessor is that it was designed to fit into existing desktop designs for Pentium branded CPUs. It was marketed as a product which could perform as well as its Intel Pentium II equivalent but at a... - Cyrix 6x86Cyrix 6x86The Cyrix 6x86 is a sixth-generation, 32-bit 80x86-compatible microprocessor designed by Cyrix and manufactured by IBM and SGS-Thomson. It was originally released in 1996.-Architecture:...

- WinChip C6WinChipThe WinChip series was a low-power Socket 7-based x86 processor designed by Centaur Technology and marketed by its parent company IDT.-Design:The design of the WinChip was quite different from other processors of the time...

- NexGen Nx586

- Rise mP6MP6This article is about the mP6 microprocessor. The Rise mP6 was a superpipelined and superscalar microprocessor designed by Rise Technology to compete with the Intel Pentium line.-History:...

External links

- CPU-Collection.de - Intel Pentium images and descriptions

- Plasma Online Intel CPU Identification

- Pictures of all known Pentium chips at chipdb.org

- The Pentium Timeline Project The Pentium Timeline Project maps oldest and youngest chip known of every s-spec made. Data are shown in a interactive timeline.

Intel Datasheets

- Pentium (P5)

- Pentium (P54)

- Pentium MMX (P55C)

- Mobile Pentium MMX (P55C)

- Mobile Pentium MMX (Tillamook)

Intel Manuals

These Manuals do provide a overview of the Pentium Processor and its features:- Pentium® Processor Family Developer’s Manual Pentium® Processor (Volume 1) (Intel Order Number 241428)

- Pentium® Processor Family Developer’s Manual [ftp://download.intel.com/design/pentium/manuals/24319101.PDF Volume 2: Instruction Set Reference] (Intel Order Number 243191)

- Pentium® Processor Family Developer’s Manual [ftp://download.intel.com/design/pentium/manuals/24143004.pdf Volume 3: Architecture and Programming Manual] (Intel Order Number 241430)